单晶金刚石凭借优异的力、热、光、电等性质,在探测器、功率器件、量子计算等领域具有广泛的应用前景,但大尺寸低缺陷高纯度晶体的合成是制约其应用的主要瓶颈。作为两种最常用的CVD手段,异质外延工艺相比同质外延工艺,由于不受籽晶尺寸的限制,在大尺寸单晶金刚石制备方面具有更显著的技术优势。

异质外延单晶金刚石合成工艺涉及异质衬底选择、金刚石高密度形核、金刚石外延生长等过程,而Ir复合衬底和偏压增强形核工艺是目前最优的异质衬底和形核手段。然而,由于受到Ir衬底-金刚石界面晶格失配的影响,所合成的金刚石往往表现出较高的位错密度,这对其在电子器件领域的应用十分不利。因此,如何降低异质外延单晶金刚石中的位错密度是该领域近年来研究的重要课题。

近日,哈尔滨工业大学朱嘉琦教授团队在开展单晶金刚石异质外延生长研究工作的基础上,对该领域的研究进展进行了详细总结,在《新型炭材料》(New Carbon Materials)上发表最新综述“Recent progress on controlling dislocation density and behavior during heteroepitaxial single crystal diamond growth”。

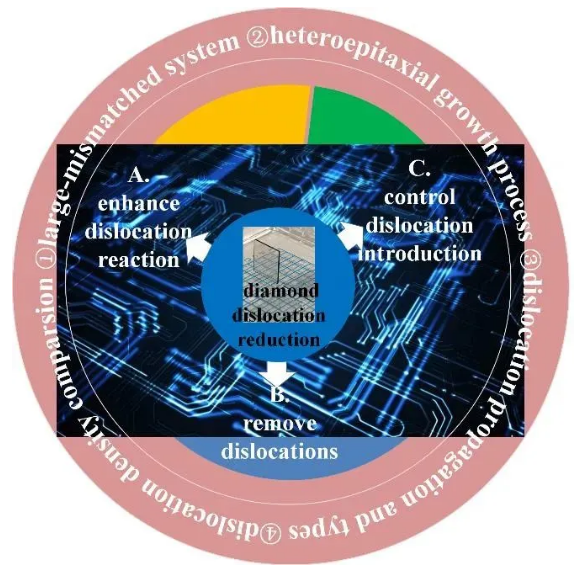

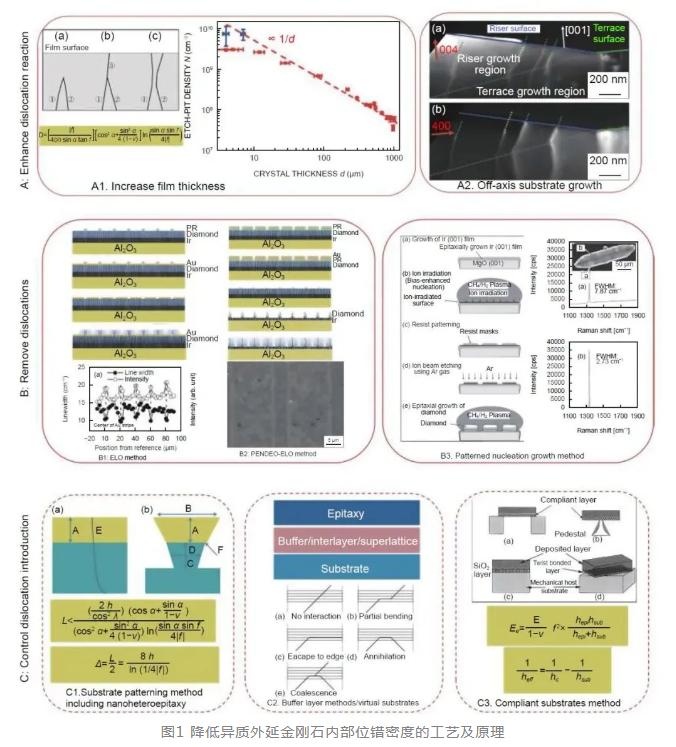

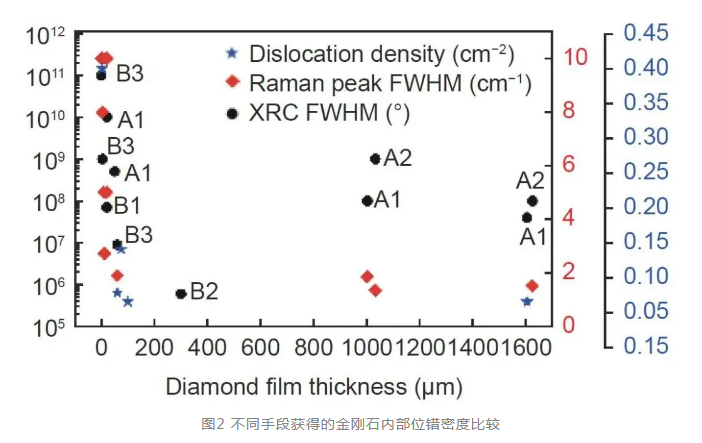

该文以降低Ir 衬底上异质外延金刚石膜中位错密度为目标,首先对该过程中的位错产生、类型、表征等进行阐释,然后从理论与工艺相结合的角度总结了加剧位错反应(增加外延层厚度,偏轴衬底生长)、除去已有位错(横向外延过度生长,悬挂-横向外延生长,图形化形核生长)及其他方法(三维生长法、金属辅助终止法、采用金字塔型衬底法)在降低金刚石位错密度方面的最新进展,随后结合大失配异质外延半导体体系降低位错密度的经典理论,提出了衬底图形化技术、超晶格缓冲层技术和柔性衬底技术等可通过抑制引入位错来进一步降低位错密度的研究方向,最后对本领域的发展现状和未来展望进行了总结。如图1所示为该文总结的降低异质外延金刚石内部位错密度的具体手段。如图2所示为目前所采用上述手段获得的金刚石内部位错密度比较,可以发现金刚石膜内位错密度任然处于较高水平,尚需开发新一代位错密度降低技术。

哈尔滨工业大学博士研究生王伟华为第一作者,朱嘉琦教授为共同通讯作者。上述研究得到了国家重点研发计划、广东省重点研发计划、国家杰出青年基金和国家自然科学基金的支持。